# SOC Design

# Week 3: ZYNQ Architecture

**Fenerbahçe University**

#### Professor & TAs

Prof: Dr. Vecdi Emre Levent

Office: 311

Email: emre.levent@fbu.edu.tr

TA: Arş. Gör. Ezgi Çakmak

Office: 311

Email: ezgi.cakmak@fbu.edu.tr

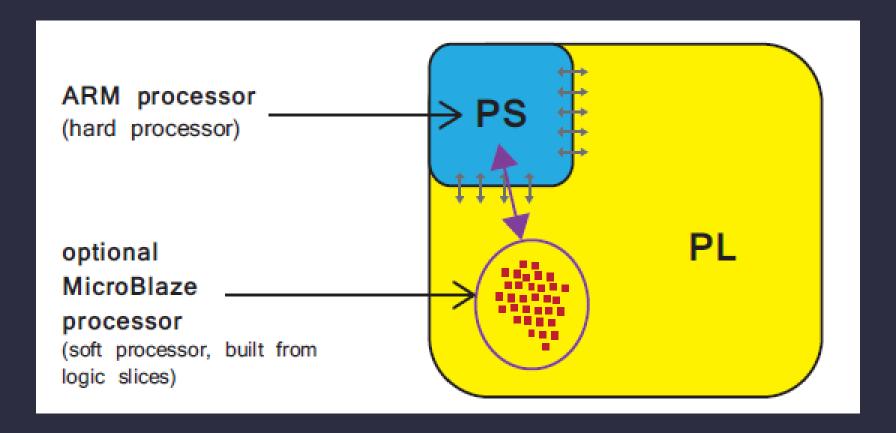

- ARM Cortex A9

- Softcore Microblaze

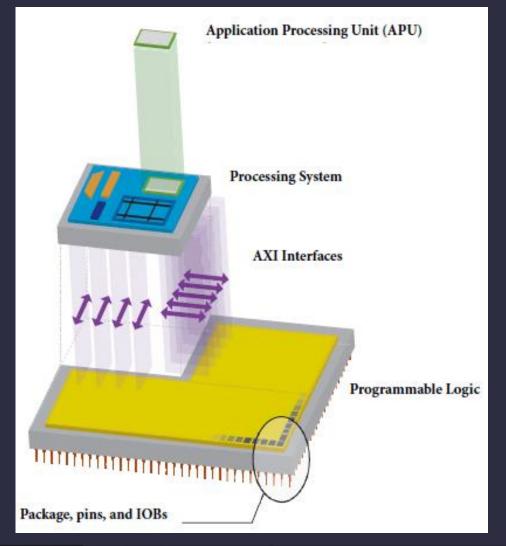

#### **ZYNQ** Architecture

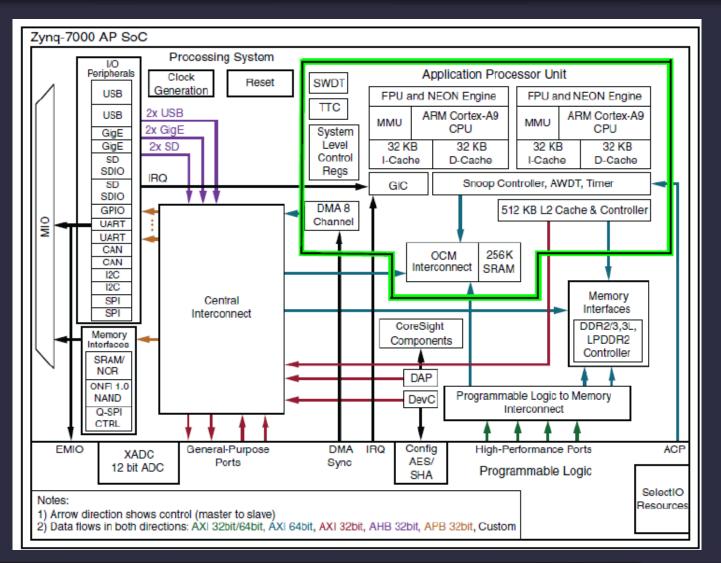

- MIO: Selects which pin the signals in the I/O interface of the Multiplexed I/O APU will be directed to.

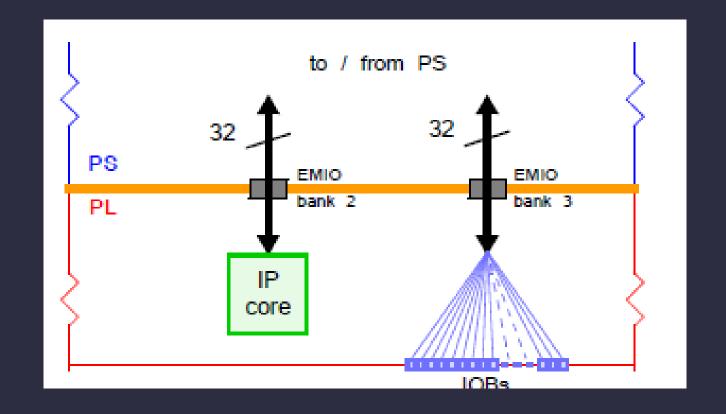

- **EMIO**: Extended Multiplexed I/O ensures that the desired interface is directed to the PL section.

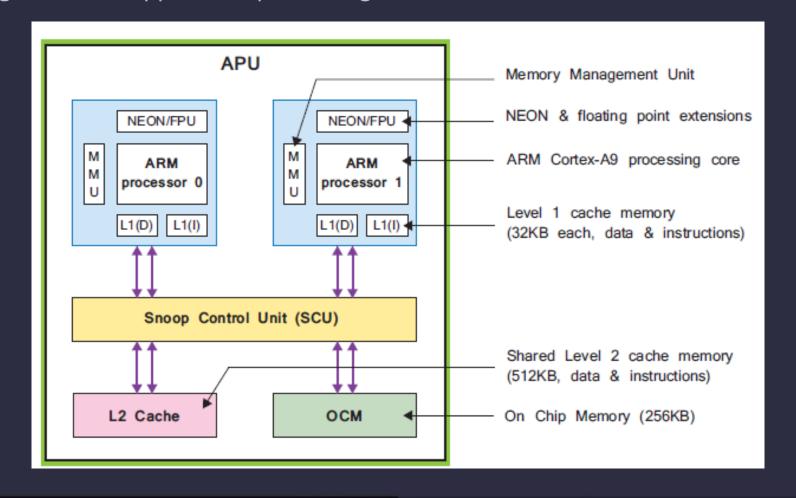

- APU: It is the part where the core of the processor is located.

- **General Purpose Ports**: It is the recommended port for low speed data transfer.

- **High Performance Ports**: It is the preferred port for high speed data transfer. IRQ: It is the port that the PL drives to create an interrupt to the processor.

- **ACP**: It has the same features as the HP port. However, it works consistently with the processor's cache (Cache Coherence).

• Block diagram of the application processing unit

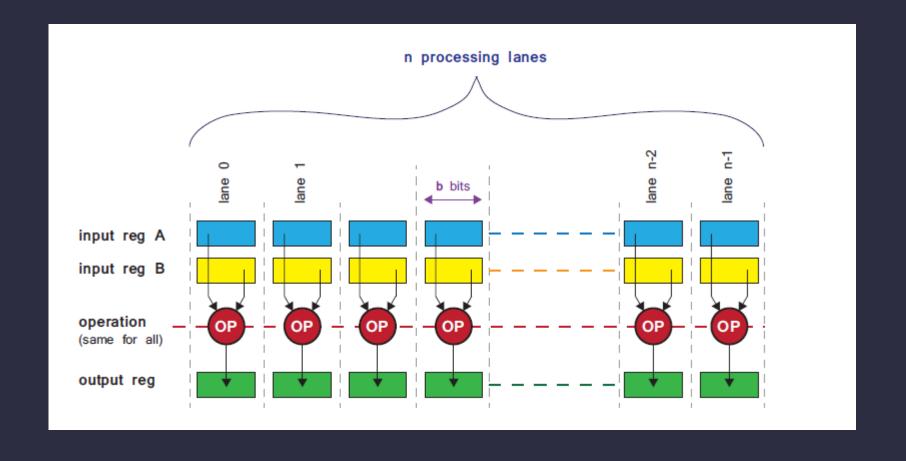

• Single Instruction Multiple Data (SIMD) processing in the NEON MPE

- List of I/O Peripheral Interfaces

- SPI (x2)

- 12C (x2)

- CAN (x2)

- UART (x2)

- GPIO

- SD (x2)

- USB (x2)

- GigE (x2)

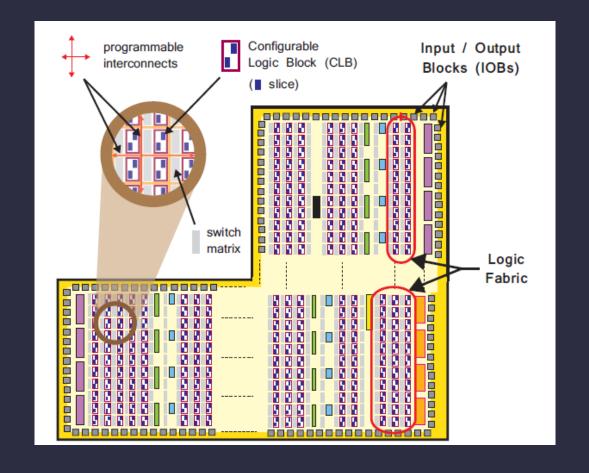

• The logic fabric and its constituent elements

• Using the EMIO to interface between PS and PL

Interfaces between PS and PL

| Interface Name | Interface Description                                                                                       | Master | Slave |

|----------------|-------------------------------------------------------------------------------------------------------------|--------|-------|

| M_AXI_GP0      | a In (AM an)                                                                                                | PS     | PL    |

| M_AXI_GP1      | General Purpose (AXI_GP)                                                                                    | PS     | PL    |

| S_AXI_GP0      | a In (AM an)                                                                                                | PL     | PS    |

| S_AXI_GP1      | General Purpose (AXI_GP)                                                                                    | PL     | PS    |

| S_AXI_ACP      | Accelerator Coherency Port (ACP),<br>cache coherent transaction                                             | PL     | PS    |

| S_AXI_HP0      | High Performance Ports (AXI_HP) with                                                                        | PL     | PS    |

| S_AXI_HP1      | read/write FIFOs.  (Note that AXI_HP interfaces are sometimes referred to as AXI Fifo Interfaces, or AFIs). | PL     | PS    |

| S_AXI_HP2      |                                                                                                             | PL     | PS    |

| S_AXI_HP3      | referred to as AAI Filo Interfaces, of AFIS).                                                               | PL     | PS    |

• Zynq-7000 family members

|                                                        | Z-7010                                               | Z-7015           | Z-7020           | Z-7030                    | Z-7045                    | Z-7100             |  |

|--------------------------------------------------------|------------------------------------------------------|------------------|------------------|---------------------------|---------------------------|--------------------|--|

| Processor                                              | Dual core ARM Cortex-A9 with NEON and FPU extensions |                  |                  |                           |                           |                    |  |

| Max. processor clock frequency                         | 866MHz                                               |                  |                  | 1GHz                      |                           |                    |  |

| Programmable<br>Logic                                  | Artix-7                                              |                  |                  | Kintex-7                  |                           |                    |  |

| No. of FlipFlops                                       | 35,200                                               | 96,400           | 106,400          | 157,200                   | 437,200                   | 554,800            |  |

| No. of 6-input<br>LUTs                                 | 17,600                                               | 46,200           | 53,200           | 78,600                    | 218,600                   | 277,400            |  |

| No. of 36Kb Block<br>RAMs                              | 60                                                   | 95               | 140              | 265                       | 545                       | 755                |  |

| No. of DSP48 slices<br>(18x25 bit)                     | 80                                                   | 160              | 220              | 400                       | 900                       | 2020               |  |

| No. of SelectIO<br>Input/Output<br>Blocks <sup>a</sup> | HR: 100<br>HP: 0                                     | HR: 150<br>HP: 0 | HR: 200<br>HP: 0 | HR: 100<br>HP: 150        | HR: 212<br>HP: 150        | HR: 250<br>HP: 150 |  |

| No. of PCI Express<br>Blocks                           | -                                                    | 4                | -                | 4                         | 8                         | 8                  |  |

| No. of serial<br>transceivers                          | -                                                    | 4                | -                | 4                         | 8 or 16 <sup>b</sup>      | 16                 |  |

| Serial transceivers<br>maximum rate                    | -                                                    | 6.25Gbps         | -                | 6.6Gbps/<br>12.5Gbps<br>c | 6.6Gbps/<br>12.5Gbps<br>b | 10.3Gbps           |  |

General ZYNQ Architecture