Midterm

- Midterm Sample Questions

- Midterm Questions

- Midterm Solutions

Final

| Topics | Topic |

|---|---|

| 1 | Safety Critical Interfaces |

| 2 | Security of Interfaces |

| 3 | Safety Critical OS |

| 4 | RISC-V AI Applications |

| 5 | RISC-V Quantum Applications |

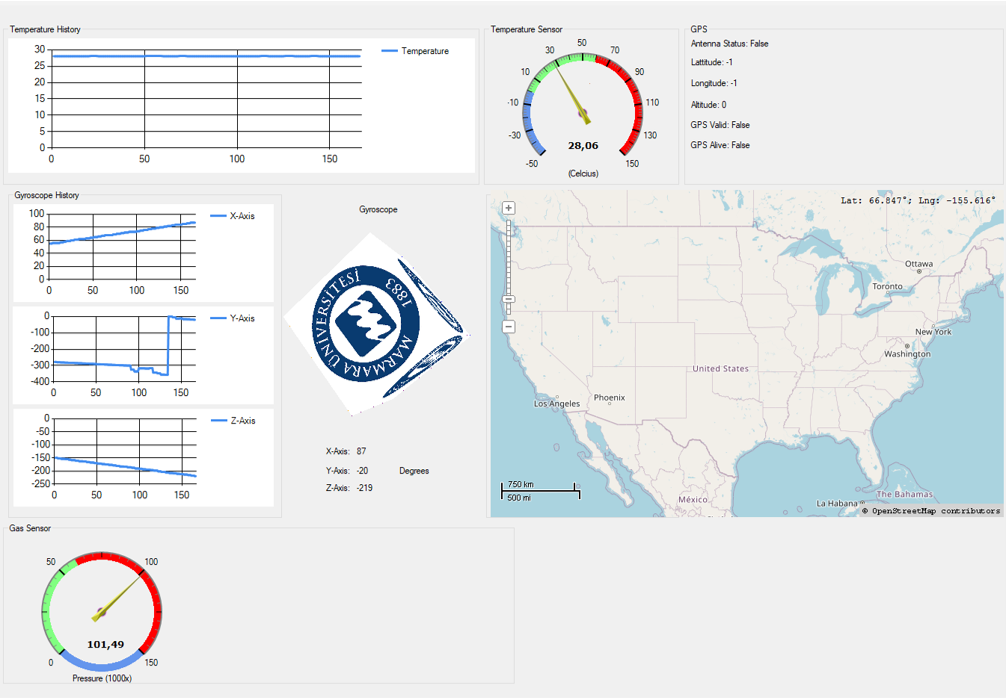

| 6 | Gyro Drift Compensation |

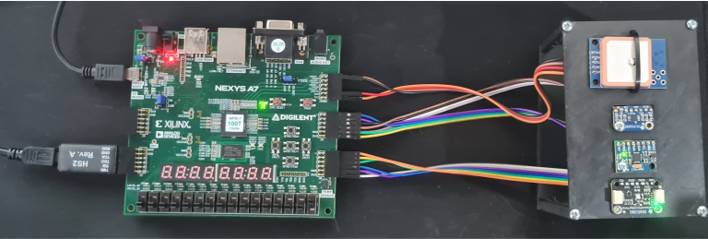

Bu ders kapsamında, gömülü sistem uygulamalarında kullanılan MCU ve MPU mimarileri incelenecek ve çeşitli gömülü sistem uygulamaları geliştirilecektir. Dersin ilk bölümünde, sektörde yaygın olarak kullanılan MCU ve MPU’lar ile çeşitli sensörler entegre edilerek sistem tasarımı yapılacaktır. Dersin ikinci bölümünde ise, dünyanın en popüler açık kaynaklı işlemci mimarisi olan RISC-V tabanlı bir işlemci tasarlanacak ve doğrulaması gerçekleştirilecektir. Tasarım sürecinde Verilog ve SystemVerilog dilleri kullanılacak, doğrulama ise SystemVerilog ile yapılacaktır. Tasarlanan işlemciye UART, I2C, SPI gibi yaygın kullanılan arayüzler entegre edilecek; sıcaklık, GPS ve IMU gibi sensörlerle çalışan gömülü sistem uygulamaları geliştirilerek demoları gerçekleştirilecektir. RISC-V tabanlı geliştirmeler esnasında Xilinx Artix-7 FPGA’ler kullanılacaktır.

TBA

Assist. Prof. Vecdi Emre Levent

There are no prerequisites.

Reference sources of the course are listed below.

Xilinx Vivado 2024.2

The course has 3 hours of theory per week. It is expected that the course materials given by the lecturer will be reviewed before the lesson and repeated after the lesson.

There will be two quizzes during the semester. 30 minutes will be given. Quiz date will be announced one week in advance.

It is mandatory to attend classes at 80%.

Term grade; will be determined by midterm, labs, assignments, project and final exam. Evaluation percentages are given in the table below.

| Activities | Rates |

|---|---|

| Midterm | %30 |

| Homework/Quiz/Seminar | %20 |

| Final | %40 |

5 points will be deducted for each hour that passes over the delivery time of homework and quizzes.

The weight and letter grade corresponding to the end of term grade are given in the table below.

| Mark | Weight | Letter grade |

| 90-100 | 4.00 | AA |

| 85-89 | 3.50 | BA |

| 80-84 | 3.00 | BB |

| 75-79 | 2.50 | CB |

| 65-74 | 2.00 | CC |

| 50-64 | 1.50 | DC |

| 45-49 | 1.00 | DD |

| 0 -44 | 0 | FF |

The effort table that the student is expected to show during the term is given below.

| Content | Hours | Times | Sub Total |

| Lesson Preparation | 2 | 14 | 28 |

| Lesson Repetition | 2 | 14 | 28 |

| Homeworks | 4 | 4 | 16 |

| Course Lesson | 3 | 15 | 45 |

| Midterm and Final | 24 | 2 | 48 |

Students are expected to spend an average of 165 hours during the semester to be successful in the course.

Grading of coding assignments will be done by examining the accuracy, quality and details of the algorithmic implementation of the code.

Test entry and expected outputs will be shared for each assignment to be given. However, other test situations that have not been shared with you will be tried during the homework control. Code that takes longer to run than expected may be evaluated incorrectly.

The code should be the design of the desired algorithm. The optimal solution is not expected. But memory and runtime shouldn’t be too much than expected.

The assignment should be written in your own handwriting. The homework answer sheet should contain the name of the course, student name and surname, student number and date.

The aim of the homework is to learn to do in-depth research about the course and to gain practical knowledge. Working with other students on assigned assignments is encouraged. Students who form a study group are more successful in exams than students who study on their own.

But even if you work with others to solve an assignment, you must solve each problem yourself without help. If you obtain your solution through a search (eg an internet search), you should express the solution in your own sentence and/or code. When the solution is asked orally, the student is expected to be able to explain it.

If the given assignment is a code, you have to write it yourself. You can get help from others in debugging. Manual and automatic mechanisms will be used for plagiarism detection in code. Plagiarism, cheating in the exam and similar behaviors are punished according to the disciplinary regulations.

Course Description: Bu ders kapsamında, gömülü sistem uygulamalarında kullanılan MCU ve MPU mimarileri incelenecek ve çeşitli gömülü sistem uygulamaları geliştirilecektir. Dersin ilk bölümünde, sektörde yaygın olarak kullanılan MCU ve MPU’lar ile çeşitli sensörler entegre edilerek sistem tasarımı yapılacaktır. Dersin ikinci bölümünde ise, dünyanın en popüler açık kaynaklı işlemci mimarisi olan RISC-V tabanlı bir işlemci tasarlanacak ve doğrulaması gerçekleştirilecektir. Tasarım sürecinde Verilog ve SystemVerilog dilleri kullanılacak, doğrulama ise SystemVerilog ile yapılacaktır. Tasarlanan işlemciye UART, I2C, SPI gibi yaygın kullanılan arayüzler entegre edilecek; sıcaklık, GPS ve IMU gibi sensörlerle çalışan gömülü sistem uygulamaları geliştirilerek demoları gerçekleştirilecektir. RISC-V tabanlı geliştirmeler esnasında Xilinx Artix-7 FPGA’ler kullanılacaktır.

| Hafta | Ders |

|---|---|

| 1 | Giriş |

| 2 | MCU, MPU, FPGA Mimarileri, Arayüzler |

| 3 | Sensörler ile Sistem Tasarımı I, Baremetal |

| 4 | Sensörler ile Sistem Tasarımı II, FreeRTOS |

| 5 | Sensörler ile Sistem Tasarımı III, Embedded Linux |

| 6 | RTL Tasarım I (Kombinasyonel Devreler) |

| 7 | RTL Tasarım II (Ardışık Devreler, Durum Makinaları) |

| 8 | RTL Tasarım III (Bellekler, Çoklu Clock Tasarımları ve SoC Konseptleri) + Temel Doğrulama |

| 9 | Midterm |

| 10 | AXI Arayüzleri ve AXI Arayüzlü Özel Donanım Geliştirme |

| 11 | System Verilog Tabanlı Doğrulama |

| 12 | RISC-V Mimarisi ve CV32E40P MCU Çekirdeği |

| 13 | RISC-V Baremetal Derleyicileri ve FreeRTOS |

| 14 | Çevre birimleri (GPIO, UART, Timer, I2C, QSPI, JTAG) ve Bellek Yapılandırmaları I + Sensörler |

| 15 | Çevre birimleri (GPIO, UART, Timer, I2C, QSPI, JTAG) ve Bellek Yapılandırmaları II + Sensörler |

| 16 | Fiziksel Çip Tasarım Süreci (OpenLane Araçları) |

| 17 | Final |

Course Description: This course covers basic logic gates, combinatorial and sequential circuits, finite state machines, memories, RISC-V processor instruction set, pipelining and performance, RISC, CISC, ISA, assembler, linker, loader, caches, virtual memory, interrupts, parallelism It includes the topics of input and output elements. Within the scope of the course, the control and ALU blocks of a RISC-V processor, whose initial design is given, will be designed and verified using the basic SystemVerilog language features.

Midterm

Final

A question and answer system is offered where students can ask questions and get answers. It is a platform for course announcements, student questions and answers. You can access it below.

https://piazza.com/class/l92ben0xzvd6eh

LMS (Learning Management System), some assignments will be required to be delivered through the LMS system.